El avance de la electrónica ha estado guiado durante décadas por una máxima sencilla: más pequeño es mejor. Desde los años 60, cada nueva generación de microchips ha incrementado la cantidad de transistores en un espacio reducido, cumpliendo con la conocida ley de Moore. Esta ley, propuesta por el cofundador de Intel, Gordon Moore, en 1965, predecía que el número de componentes en un microchip se duplicaría aproximadamente cada año. Sin embargo, esta tendencia hacia la miniaturización enfrenta límites físicos. En respuesta, un equipo internacional de científicos ha propuesto una solución innovadora: en lugar de seguir reduciendo el tamaño de los chips, se deben construir en vertical.

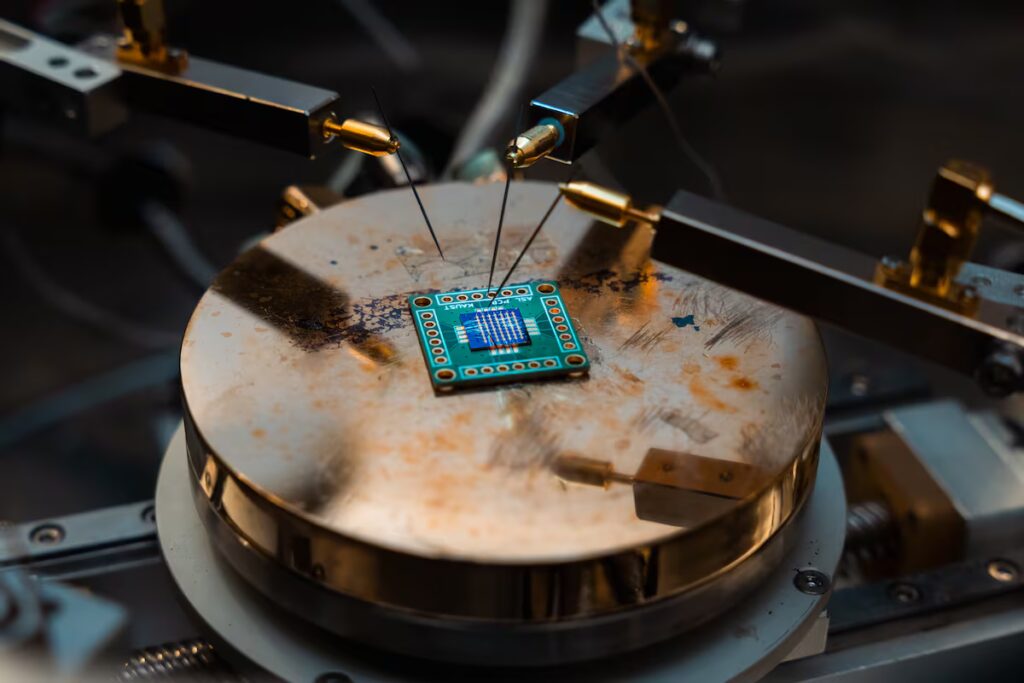

Xiaohang Li, investigador de la Universidad de Ciencia y Tecnología Rey Abdullah de Arabia Saudí (KAUST), junto a su equipo, ha desarrollado un chip con 41 capas verticales de semiconductores y materiales aislantes, aproximadamente diez veces más alto que los chip fabricados anteriormente. Este trabajo se publicó en la revista Nature Electronics y representa un avance técnico significativo, abriendo la puerta a una nueva generación de dispositivos electrónicos flexibles y sostenibles.

Aumento de Densidad y Rendimiento

“Apilar seis o más capas de transistores verticalmente nos permite incrementar la densidad de circuitos sin reducir su tamaño lateral”, explica Li. “Con seis capas, conseguimos integrar un 600% más de funciones lógicas en la misma área que con una única capa, logrando así un mayor rendimiento y un menor consumo energético”.

La ley de Moore comenzó a declinar en su efectividad desde 2010, cuando los fabricantes de chips se enfrentaron a problemas relacionados con la física. Los transistores actuales son tan pequeños, del orden de unos nanómetros, que los efectos cuánticos interfieren en su funcionamiento. “Aunque la ley de Moore está alcanzando sus límites en la microelectrónica de silicio convencional, la innovación sigue su curso en otras direcciones. En vez de seguir reduciendo los transistores, estamos investigando nuevos materiales, arquitecturas y posibilidades como el apilamiento”, señala Li.

Desafíos en la Fabricación

Para entender el desafío técnico que enfrentó el equipo, Li utiliza una metáfora arquitectónica: “Imagine cada capa de transistores como un piso de un rascacielos; si un piso está irregular, toda la estructura puede volverse inestable”. La clave del éxito del experimento fue dominar lo que llaman la “rugosidad de la interfaz”, ya que cualquier imperfección entre capas puede interrumpir el flujo de electrones y afectar drásticamente el rendimiento del chip.

Un avance crucial fue desarrollar nuevas estrategias de fabricación. Se centraron en asegurar que todas las capas se depositaran a temperatura ambiente o cercana, lo que protege las capas inferiores. Esta manufactura a baja temperatura no es solo un detalle técnico; “la mayoría de los materiales flexibles no soportan altas temperaturas”, aclara Li. Los procesos tradicionales de semiconductor suelen exceder los 400 °C, lo que podría dañar estos materiales. Así, mantener un proceso cerca de la temperatura ambiente permite utilizar sustratos plásticos, facilitando el camino hacia la electrónica flexible del futuro.

Rendimiento y Aplicaciones Futuras

Para validar su diseño, el equipo fabricó 600 copias del chip, todas con un rendimiento similar. Utilizando estos chips apilados, implementaron operaciones básicas y lograron un rendimiento comparable al de chips convencionales no apilados, pero con un consumo energético notablemente inferior: solo 0,47 microvatios frente a los 210 típicos de dispositivos actuales.

¿Cuáles serán las primeras aplicaciones de esta tecnología? Li es optimista pero consciente: “Las primeras aplicaciones probablemente incluirán sensores de salud, etiquetas inteligentes y pantallas flexibles, donde el bajo consumo y la flexibilidad son esenciales”. A largo plazo, el equipo imagina «pieles electrónicas» que podrían procesar y comunicar información en grandes superficies. Aunque es poco probable que estos chips alimenten supercomputadoras, su integración en electrodomésticos podría reducir la huella de carbono de la industria electrónica.

“Los circuitos que desarrollamos están diseñados para sistemas donde la flexibilidad, el bajo costo y la escalabilidad son más importantes que la velocidad extrema”, concluye Li. Su investigación marca una nueva etapa en la informática, mostrando que el rendimiento puede continuar escalando no solo haciendo los dispositivos más pequeños, sino integrándolos de forma más inteligente y eficiente en tres dimensiones.